コンパレータ回路

2018年11月21日にて現在のURLは次のURLに移行しました。

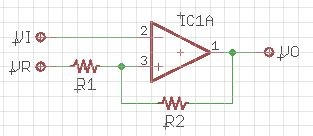

[回路図]

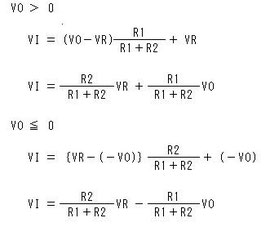

[計算式]

① 出力VOの状態により、VIの反転

電圧が変化します。

VIの反転電圧差を、ヒステリシス電圧

と呼びます。

② VO>0の場合の、VIの反転電圧

VO≦0の場合の、VIの反転電圧

を右式に示します。

③ R1とR2の比により、ヒステリシス電圧

が決定されます。

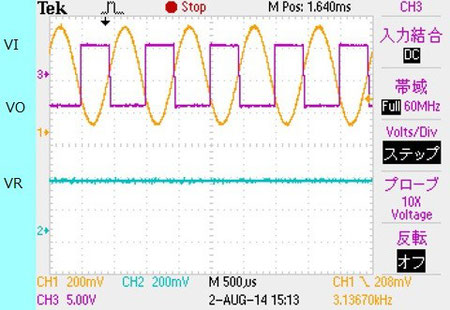

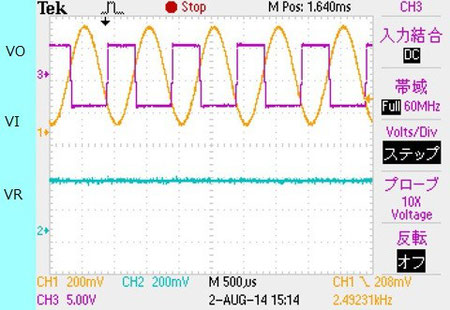

[信号波形]

IC1=OPA4277PA R1=10 KΩ R2=1 MΩ

出力VOのVL→VH反転電圧VI(L-H)と、

出力VOのVH→VL反転電圧VI(H-L)の差電圧

Vhys(ヒステリシス電圧)=約 150 [mV]

IC1=OPA4277PA R1=10 KΩ R2=500 KΩ

Vhys(ヒステリシス電圧)=約 220 [mV]

抵抗R2とVhys(ヒステリシス電圧)は、反比例の関係となります。

実験室_道具箱

実験室_道具箱